1 ę²čį

ļSų°╬óļŖūė╝╝ąg┼cėŗ╦ŃÖC╝╝ągĄ─╚šęµ│╔╩ņŻ¼ļŖūėįOėŗūįäė╗»(EDA)╝╝ągį┌ļŖūė«aŲĘ┼c╝»│╔ļŖ┬Ę(IC)ąŠŲ¼╠žäe╩Ūå╬Ų¼╝»│╔(SoC)ąŠŲ¼Ą─įOėŗæ¬ė├ųą’@Ą├įĮüĒįĮųžę¬ĪŻEDA╝╝ąg▓╔ė├“ūį╔Žų┴Ž┬”Ą─įOėŗ╦╝ŽļŻ¼į╩įSįOėŗ╚╦åT─▄ē“Å─ŽĄĮy╣”─▄╝ē╗“ļŖ┬Ę╣”─▄╝ē▀Mąą«aŲĘ╗“ąŠŲ¼Ą─įOėŗŻ¼ėą└¹ė┌«aŲĘį┌ŽĄĮy╣”─▄╔ŽĄ─ŠC║Žā×╗»Ż¼Å─Č°╠ßĖ▀┴╦ļŖūėįOėŗĒŚ─┐Ą─ģfū„ķ_░lą¦┬╩Ż¼ĮĄĄ═ą┬«aŲĘĄ─čą░l│╔▒ŠĪŻ

Į³╩«─ĻüĒŻ¼EDAļŖ┬ĘįOėŗ╝╝ąg║═╣ż│╠╣▄└ĒĘĮ├µĄ─░lš╣ų„ę¬│╩¼F│÷ā╔éĆ┌ģä▌Ż║

(1)ļŖ┬ĘĄ─╝»│╔╦«ŲĮęčĮø▀M╚ļ┴╦╔Ņüå╬ó├ūĄ─ļAČ╬Ż¼ŲõÅ═ļs│╠Č╚ęį├┐─Ļ58%Ą─Ę∙Č╚čĖ╦┘į÷╝ėŻ¼ąŠŲ¼įOėŗĄ─│ķŽ¾īė┤╬įĮüĒįĮĖ▀Ż¼Č°«aŲĘĄ─čą░lĢrŽ▐ģs▓╗öÓ┐sČ╠ĪŻ

(2)ICąŠŲ¼Ą─ķ_░l▀^│╠ę▓╚š┌ģÅ═ļsĪŻÅ─Ū░Ų┌Ą─š¹¾wįOėŗĪó╣”─▄äØĘųŻ¼ĄĮŠ▀¾wĄ─▀ē▌ŗŠC║ŽĪóĘ┬šµ£yįćŻ¼ų▒ų┴║¾Ų┌Ą─ļŖ┬ĘĘŌčbĪó┼┼░µ▓╝ŠĆŻ¼Č╝ąĶę¬Ę┤Å═Ą─“×ūC║═ą▐Ė─Ż¼å╬┐┐éĆ╚╦┴”┴┐¤oĘ©═Ļ│╔ĪŻICąŠŲ¼Ą─ķ_░lęčĮøīŹąąČÓ╚╦ĘųĮMģfū„ĪŻ

ė╔┤╦┐╔ęŖŻ¼╚ń║╬╠ßĖ▀įOėŗĄ─│ķŽ¾īė┤╬Ż¼į┌▌^Č╠Ģrķgā╚įOėŗ│÷▌^Ė▀ąį─▄Ą─ąŠŲ¼Ż¼╚ń║╬Ė─▀MEDA╣ż│╠╣▄└ĒŻ¼▒ŻūCąŠŲ¼į┌ČÓĮMģfū„įOėŗŽ┬Ą─╝µ╚▌ąį║═ĘĆČ©ąįŻ¼ęčĮø│╔×ķ«öŪ░EDA╣ż│╠ųąūŅ╩▄ĻPūóĄ─å¢Ņ}ĪŻ

ßśī”▀@ą®å¢Ņ}Ż¼╚╦éā╠ß│÷┴╦▄øė▓╝■ģf═¼Į©─ŻįOėŗ3Ą─╦╝ŽļŻ¼īóĮyę╗Į©─ŻšZčį(UML)┼cSoCįOėŗ┴„│╠ŽÓĮY║ŽŻ¼«a╔·┴╦ą┬ą═Ą─SoCįOėŗĘĮĘ©Ż¼═¼Ģrī”EDA╣ż│╠Ą─ĘųĮMģfū„▓╔ė├īė┤╬╗»╣▄└ĒŻ¼╠ßĖ▀┴╦ąŠŲ¼čą░lłFĻĀĄ─ģfš{║Žū„─▄┴”Ż¼▀Mę╗▓Į╝ė┐ņSoC«aŲĘĄ─ķ_░l╦┘Č╚ĪŻ▒Š╬─Å─Į©─ŻĄ─╦╝Žļ│÷░lŻ¼ų„ę¬ĻU╩÷┴╦ĮY║ŽUMLĮ©─Ż╝╝ągĄ─ą┬ą═SoCįOėŗ┴„│╠Ą─įŁ└Ē╝░Ųõā×ä▌Ż¼ĮķĮB┴╦ų¦│ųSystemCĄ─UML╝▄śŗ╝░Ųõæ¬ė├Ż¼ūŅ║¾ßśī”EDA╣ż│╠Ą─ĘųĮMģfū„Ą─╣▄└Ēå¢Ņ}Ż¼ĮķĮB┴╦ę╗ĘNīė┤╬╗»╣▄└ĒĄ─įŁ└Ē║═Ė─▀MĘĮ░ĖĪŻ

2 ╗∙ė┌UMLĮ©─ŻĄ─SoCįOėŗĘĮĘ©

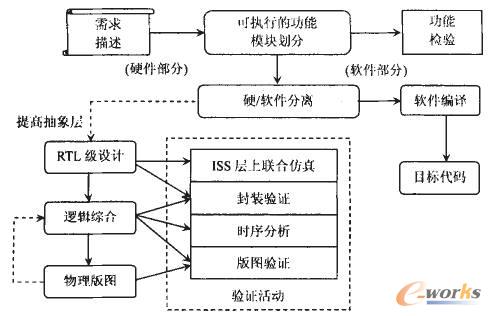

SoCįOėŗĄ─ĻPµIį┌ė┌«ÉŅÉ─ŻēKų«ķgĄ─ģfū„╝µ╚▌│╠Č╚ęį╝░▀@ą®─ŻēKį┌Ė▀│ķŽ¾īė┤╬╔ŽĄ─╣żū„─▄┴”ĪŻ│ŻęÄĄ─SoCįOėŗ▀^│╠Ż¼╚ńłD1╦∙╩ŠŻ¼╩ŪÅ─ūŅ│§Ą─ŽĄĮyĄ─ąĶŪ¾├Ķ╩÷ķ_╩╝Ą─Ż¼╚╗║¾Ė∙ō■įōąĶŪ¾├Ķ╩÷Ż¼ŽĄĮy▒╗äØĘų│╔ČÓéĆ╣”─▄─ŻēKŻ¼└²╚ń┤µā”Ų„▓┐ĘųŻ¼Ę┼┤¾Ų„▓┐ĘųĄ╚ĪŻ╣”─▄äØĘųĄ─š²┤_ąįŻ¼īóį┌▌^Ė▀īė┤╬Ą─╣”─▄Ę┬šµųąĄ├ĄĮÖz“×ĪŻ

łD1 │ŻęÄĄ─SoCįOėŗ┴„│╠

╣”─▄äØĘųų«║¾Ż¼ŽĄĮy▀M╚ļūŅųžę¬Ą─▄øė▓╝■ĘųļxļAČ╬Ż¼Ęųļxķ_Ą─ė▓╝■║═▄ø╝■▓┐ĘųėąŲõĖ„ūįĄ─įOėŗ┴„│╠ĪŻ═©│ŻŻ¼▄ø╝■▓┐Ęų╩╣ė├│╠ą“šZčįŻ©╚ńC/C++Ż®ŠÄīæ┤·┤aŻ¼ą╬│╔─┐ś╦╬─╝■║¾╝┤┐╔▀MąąĘ┬šµ£yįćĪŻČ°ė▓╝■▓┐Ęų▒╗Ęųļx│÷üĒų«║¾Ż¼ąĶę¬▀Mę╗▓Į╝Ü╗»Īó│ķŽ¾▓┼─▄▀M╚ļ╝─┤µŲ„é„▌ö╝ē(RTL)Ą─├Ķ╩÷ļAČ╬ĪŻį┌▀@éĆļAČ╬Ż¼ė▓╝■▓╔ė├ė▓╝■├Ķ╩÷šZčįŻ©╚ńHDLŻ®üĒ├Ķ╩÷Ż¼╚╗║¾═©▀^▀Mę╗▓Į▀ē▌ŗŠC║ŽŻ¼ą╬│╔│ŻęÄį¬╝■Äņ╗“ŅAČ©┴xį¬╝■ÄņųąęčėąĄ─▀ē▌ŗå╬į¬ĪŻ▀@ą®▀ē▌ŗå╬į¬ėą╣╠Č©Ą─ĘŌčbŻ¼į┘Įø▀^░µłDęÄäØŻ¼ĢrńŖ─ŻöM║═ūįäė▓╝ŠĆęį║¾Ż¼ą╬│╔ūŅĮKĄ─╬’└Ē░µłDĪŻ╚╗Č°Ż¼ė▓╝■▓┐ĘųÅ─Ęųļx│÷üĒĄĮ▀M╚ļRTL╝ēĄ─įOėŗ▀^│╠╚▒Ę”ėąą¦Ą─ŃĢĮėŻ¼ųŲ╝s┴╦SoCįOėŗ│ķŽ¾│╠Č╚Ą─╠ßĖ▀ĪŻ

į┌▀@ĘN│ŻęÄĄ─SoCįOėŗ┴„│╠ųąŻ¼▄øė▓╝■Ą─įOėŗ░³║¼┴╦ę╗ŽĄ┴ąĄ─Ę┬šµ║═“×ūC╗ŅäėŻ║ė▓╝■Ą─RTL╝ē├Ķ╩÷║═▄ø╝■Ą──┐ś╦┤·┤a═©▀^▀\ąąųĖ┴ŅįOų├Ę┬šµŲ„Ż¼Öz“×Ė„ūįISS(ųĖ┴ŅįOų├)Ą─š²┤_ąįŻ╗į┌▀ē▌ŗå╬į¬Ą─ŠC║Ž▀^│╠ųą▓╗öÓ▀MąąĘŌčb“×ūCĪóĢrą“Ęų╬÷║═░µłD“×ūCŻ╗ūŅ║¾╔·│╔Ą─╬’└Ē░µłD▀Ćę¬┼c▀ē▌ŗå╬į¬▀Mąąę╗ų┬ąįąŻ“×ĪŻĄ½╩Ūė╔ė┌▀@ą®“×ūCę¬į┌ė▓╝■Ą─RTL╝ē├Ķ╩÷║═▄ø╝■Ą──┐ś╦┤·┤aČ╝═Ļ│╔ų«║¾▓┼─▄▀MąąŻ¼ę“┤╦Öz£y│÷Ą─Õeš`═©│Ż╩Ūļyęįą▐Å═Ą─ĪŻ▀@ą®Õeš`¤oę╔īóė░ĒæĄĮąŠŲ¼į┌Ė▀│ķŽ¾īė┤╬╔ŽĄ─╣żū„ąį─▄║═Ė„─ŻēKų«ķgĄ─ģfū„Į╗╗ź─▄┴”ĪŻ

×ķ┴╦Ė─▀MSoCĄ─įOėŗŻ¼╚╦éāīó│ķŽ¾Į©─ŻĮY║ŽĄĮąŠŲ¼įOėŗ▀^│╠ųąŻ¼▓╔ė├UMIĪŻšZčį×ķąŠŲ¼įOėŗ▀^│╠▀MąąĮ©─ŻŻ¼╠ß│÷┴╦╗∙ė┌UMLĄ─SoCįOėŗĘĮĘ©ĪŻ╦¹│õĘų└¹ė├┴╦UMLČ©┴x┴╝║├Īóęūė┌▒Ē▀_Īóų¦│ųĖ„ĘN│ķŽ¾│╠Č╚Ą─ŠC║ŽĄ─ā×ä▌Ż¼Åøča┴╦│ŻęÄSoCįOėŗĘĮĘ©Ą─╔Ž╩÷▓╗ūŃĪŻ

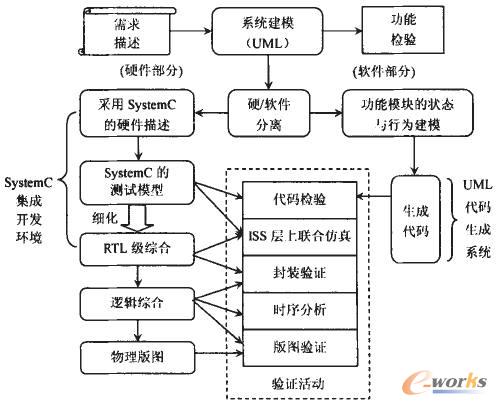

į┌▀@ĘNą┬ą═Ą─SoCįOėŗ┴„│╠ųąŻ¼╚ńłD2╦∙╩ŠŻ¼UML▒╗ė├ė┌Å─ąĶŪ¾Ęų╬÷ķ_╩╝Ą─š¹éĆąŠŲ¼ķ_░l▀^│╠ĪŻ╩╣ė├UML×ķŽĄĮyĮ©─ŻŻ¼─▄ē“ė╔║å├„ĄĮįö▒MĄž├Ķ└LŽĄĮyĄ─ąĶŪ¾ĪóĮYśŗĪó╣”─▄ęį╝░ŽÓæ¬Ą─ąą×ķŻ¼╩╣ķ_░lš▀ī”╦∙ķ_░lĄ─SoCėą£╩┤_Č°Ūę╚½├µĄ─┴╦ĮŌŻ¼Ųõ╣”─▄äØĘųĄ─š²┤_ąįę▓Ė³ęūė┌Öz“×ĪŻĮø▀^╣”─▄äØĘųŻ¼ė▓Īó▄ø╝■Ęųļxų«║¾Ż¼▄ø╝■▓┐ĘųĄ─Į©─ŻŽ╚ė╔UMLĄ─ŅÉłDĪóĀŅæBłDĪóĢrą“łDĪó╗ŅäėłDĄ╚ČÓĘNĘĮ╩ĮüĒ├Ķ╩÷Ż¼į┘═©▀^┤·┤aūįäė╔·│╔ŽĄĮyŻ¼Ą├ĄĮŽÓæ¬Ą─C/C++─┐ś╦┤·┤aĪŻ▀@▒╚ų▒ĮėŠÄīæ┤·┤aĖ³ų▒ė^Īóņ`╗ŅŻ¼ęūė┌ŠSūo║═ą▐Ė─Ż¼╩╣įOėŗš▀─▄ē“į┌▌^Ė▀īė┤╬╔ŽīŻūóė┌ąŠŲ¼Ą─š¹¾węÄäØŻ¼Č°▓╗▒ž▒╗Ą═īė┤╬Ą─┤·┤aīŹ¼F╝Ü╣Ø╦∙╩°┐`ĪŻ

Č°ė▓╝■▓┐Ęų▓╔ė├SystemCüĒ├Ķ╩÷Ż¼┐╔ęįį┌ķT╝ēĪóRTL╝ē║═ŽĄĮy╝ēĄ╚Ė„éĆ│ķŽ¾īė┤╬╔Ž║═▄ø╝■▓┐Ęųę╗Ų▀MąąĘ┬šµ║═£yįćŻ¼╩╣ķ_░lš▀─▄ē“ī”▒MįńĄž░l¼FÕeš`Ż¼į┌▀ē▌ŗå╬į¬ŠC║Žų«Ū░╝┤┐╔Ė─▀MļŖ┬ĘŻ¼╝░ĢrĮŌøQå¢Ņ}Ż¼▒ŻūC┴╦ąŠŲ¼Ą─Ė„éĆ─ŻēKį┌Ė▀│ķŽ¾īė╔ŽĄ─Į╗╗źąį─▄Ż¼═¼Ģrę▓┐sąĪ┴╦š¹éĆĘ┬šµ“×ūCĄ─╣żū„┴┐Ż¼╠ßĖ▀┴╦ę╗┤╬įOėŗĄ─│╔╣”┬╩ĪŻ

łD2 ĮY║ŽUMLĄ─ą┬ą═SoCįOėŗ┴„│╠

▀@ĘN╗∙ė┌UMLĄ─SoCįOėŗĘĮĘ©Ż¼╩╣Ą├ļŖ┬ĘįOėŗĄ─│ķŽ¾│╠Č╚Å─ŠÄīæ┤·┤a╠ßĖ▀ĄĮ┴╦ŽĄĮy╝ēĮ©─ŻĄ─īė┤╬Ż¼ā×╗»┴╦SoCĄ─įOėŗ┴„│╠Ż¼╠ßĖ▀┴╦įOėŗą¦┬╩ĪŻį┌2005─Ļš┘ķ_Ą─“UML for SoC Design Workshop 2005”Ģ■ūh╔ŽŻ¼ęŌĘ©░ļī¦¾w(ST)Š═░l▓╝┴╦▀mė├ė┌įōĘĮĘ©Ą─ė╔ąŠŲ¼Ą─UML─Żą═ūįäė╔·│╔SystemC┤·┤aĄ─EDAŽĄĮyŻ¼Ž┬├µŠ▀¾wĮķĮB▀@ĘN╣żŠ▀Ą─īŹ¼F╝▄śŗĪŻ

3 ų¦│ųSystemCĄ─UML╝▄śŗ

UMLšZčįī”C/C++Ż¼JAVAĄ╚ŠÄ│╠šZčįŠ▀ėą║▄ÅŖĄ─ų¦│ų─▄┴”Ż¼Č°SystemC╩Ū╗∙ė┌C++šZčįĄ─▄øė▓╝■ģf═¼įOėŗšZčįŻ¼░³║¼┴╦C++ŅÉÄņ║═Ę┬šµā╚║╦ĪŻ┼cHDLŽÓ▒╚Ż¼╦¹▓╗āH─▄ē“├Ķ╩÷ąŠŲ¼Ą─ė▓╝■Ż¼▀Ć┐╔ęį├Ķ╩÷ŽĄĮyĄ─£yįćŲĮ┼_Ż¼ų¦│ų│ķŽ¾īėĄ─Ę┬šµ║═£yįćŻ¼Š▀ėą║═C++šZčįę╗śė┴╝║├Ą─öUš╣ąįĪŻų¦│ųSystemCĄ─UML╝▄śŗŻ¼╩Ūį┌UML2.0░µ▒ŠĄ─╗∙ĄA╔ŽŻ¼ĮY║Ž┴╦SystemC 2.0Ą─ŅÉÄņČ©┴x║═▒Ē▀_ęÄätŻ¼īóįŁėąĄ─UMLšZ┴xŻ©░³└©łDĘ¹Īó╝s╩°ĻPŽĄ║═ś╦ūóųĄŻ®▀Mąąę╗ŽĄ┴ąĄ─öUš╣ęį╝░╣”─▄╔ŽĄ─╠ßĖ▀Ż¼╩╣ų«┼cSystemCŽÓī”æ¬ĪŻ╦¹┐╔ęį┐┤│╔╩Ū×ķ╠ž╩ŌĄ─æ¬ė├ŅIė“Ż©╚ń¤oŠĆ═©ėŹĪóīŹĢrŽĄĮyĪó▄ø╝■£yįćĄ╚Ż®Č©ųŲĄ─Š▀ėą╠ž╩Ō╣”─▄Ą─UMLĮ©─Żķ_░l┐“╝▄ĪŻ

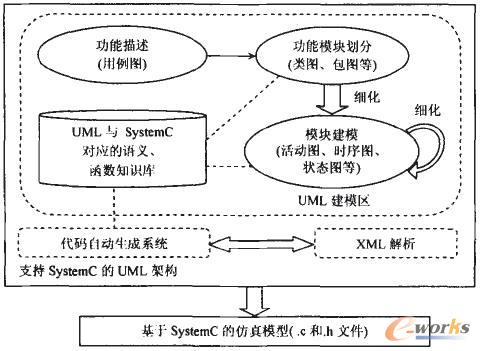

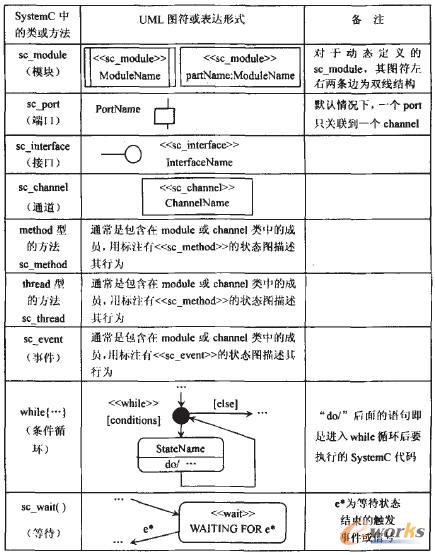

ų¦│ųSystemCĄ─UML╝▄śŗ┐é¾w┐“╝▄╚ńłD3╦∙╩ŠĪŻŲõųąŻ¼┐╔ęĢ╗»Į©─Żģ^×ķąŠŲ¼Ą─š¹¾wįOėŗĪó─ŻēKĮYśŗ║═Ė„éĆ─ŻēK╣”─▄Ą─Š▀¾wīŹ¼F╠ß╣®┴╦╣”─▄ÅŖ┤¾Ą─łDą╬╗»Į©─ŻŲĮ┼_ĪŻį┌įōŲĮ┼_╔ŽŻ¼įOėŗ╚╦åT─▄ē“į┌×ķąŠŲ¼Į©┴ó┐é¾w─Żą═Ż¼╚╗║¾ĮĶų·ė┌žSĖ╗Ą─UML─Ż░µ║═łDĘ¹Ż¼ī”Ė„éĆ╣”─▄─ŻēKĄ─Š▀¾wĮYśŗĪó─ŻēKų«ķgĄ─ŽÓ╗źĻPŽĄŻ¼ęį╝░─ŻēKā╚▓┐Ą─│╔åTŻ©░³└©ūė─ŻēKĪó│╔åT║»öĄĪó│╔åTūā┴┐Ą╚Ż®▀Mąąįö╝ÜĄ─Č©┴x║═├Ķ╩÷ĪŻ═Ļš¹Ą─UML─Żą═Į©┴ó║¾Ż¼═©▀^┤·┤aūįäė╔·│╔ŽĄĮyĄ─ĘŁūg║═▐DōQ(▀@Ų┌ķg┐╔─▄ę¬▀Mąą┐╔öUš╣ś╦ėøšZčį(XML)Ą─ĮŌ╬÷)Ż¼ūŅĮK«a╔·ė├SystemC├Ķ╩÷Ą──┐ś╦┤·┤a╬─╝■ĪŻ

łD3 ų¦│ųSystemCĄ─UML╝▄śŗĄ─┐é¾w┐“╝▄łD

į┌š¹éĆ╝▄śŗųąŻ¼UML┼cSytemCĄ─ī”欚Z┴xĪó║»öĄų¬ūRÄņ╩Ū▀BĮėUML║═SystemCĄ─ĻPµI▓┐ĘųŻ¼╦¹ų„ę¬ė╔SystemC║╦ą─ŅÉÄņĪó║╦ą─║»öĄÄņĪóöĄō■ŅÉą═Äņ║═ŅAČ©┴x═©Ą└ĪóĮė┐┌ĪóČ╦┐┌ÄņĮM│╔ĪŻ▀@ą®ŅÉÄņųąį÷įO┴╦▀m║Ž×ķSystemC│╠ą“Į©─ŻĄ─łDĘ¹║═─Ż░µŻ¼×ķUMLłDĘ¹║═SystemCšZčįų«ķg╠ß╣®┴╦├▄ŪąČ°ų▒ė^Ą─ī”æ¬ĻPŽĄĪŻłD4Įo│÷┴╦ÄūéĆ│Żė├Ą─SystemCŅÉ╗“ĘĮĘ©ęį╝░╦¹éāį┌UMLųąī”æ¬Ą─łDĘ¹╗“▒Ē▀_ą╬╩ĮĪŻ

łD4 ų¦│ųSystemCĄ─UML╝▄śŗą┬łDĘ¹Č©┴x

Ė∙ō■▀@ą®ī”æ¬ĻPŽĄŻ¼UMLĄ─ĮYśŗłDŻ©└²╚ńŅÉłDĪó░³łDĄ╚Ż®Š═┐╔ęį═©▀^▒Ē╩Š─ŻēKĪóČ╦┐┌ĪóĮė┐┌Ą╚ė▓╝■ŅÉĄ─łDĘ¹üĒ├Ķ╩÷▀@ą®ė▓╝■Ą─ĮYśŗ║═īė┤╬ĪŻČ°UMLĄ─ąą×ķłDŻ©└²╚ńĀŅæBłDĪó╗ŅäėłDĪóĢrą“łDĄ╚Ż®Š═┐╔ęįė├▒Ē╩ŠĄ╚┤²Īó裣hĄ╚ĀŅæBŅÉĄ─łDĘ¹üĒ├Ķ╩÷ė▓╝■╣”─▄Ą─Š▀¾wąą×ķ║══¼▓ĮŪķørĪŻ▀@ą®łD─▄ē“į┌Ė▀│ķŽ¾īė┤╬├Ķ╩÷SystemC▀^│╠Ż¼▓óŪę╔·│╔ėąą¦Č°║åØŹĄ─SystemC┤·┤aĪŻ

─┐Ū░Ż¼ęŌĘ©░ļī¦¾węčĮøīó▀@ĘN╝▄śŗæ¬ė├ĄĮ┴╦IEEE802.lla╬’└Ēīė▐D░l╝░╩š░lļŖ┬ĘųąĪŻ▀@ĘNĮY║ŽUMLĮ©─ŻĄ─ĘĮĘ©į┌īŹļHąŠŲ¼įOėŗæ¬ė├ųąęčĮø¾w¼F│÷▌^┤¾ā×ä▌ĪŻ▓╔ė├įōUML╝▄śŗ×ķąŠŲ¼Į©─ŻŻ¼╩╣SoCįOėŗŻ©╠žäe╩Ūė▓╝■▓┐ĘųŻ®Ą─┴„│╠Ė³▀Mę╗▓ĮÅ─RTLĄ─│ķŽ¾╔Ž╔²ĄĮŽĄĮy╝ē│ķŽ¾ĪŻ┼cRTL╝ēĄ─ų▒Įė├Ķ╩÷ĘĮĘ©ŽÓ▒╚Ż¼Į©─Ż╩╣ė▓╝■įOėŗĖ³ŽĄĮy╗»Ż¼Č°ŪęŠ▀ėą▄ø╝■įOėŗę╗śėĄ─ņ`╗Ņąį║═IP(ų¬ūR«aÖÓ)┐╔Å═ė├ąįĪŻį┌ų¦│ųSystemCĄ─UML╝▄śŗųąŻ¼╣”─▄─ŻēKĄ─Ę┬šµ║═Öz£y┐╔ęįį┌ų▒ė^Ą─Į©─Żīė┤╬╔Ž▀MąąŻ¼╩╣ąŠŲ¼Ą─Õeš`▒╚į┌RTL╝ē╔ŽĖ³╚▌ęū▒╗░l¼F║═╝mš²ĪŻ│²┤╦ęį═ŌŻ¼╩╣ė├UMLĮ©─ŻĄ─įOėŗĘĮ╩ĮĖ³▀mė├ė┌ąŠŲ¼─ŻēKį┌ČÓ╚╦ģfū„ķ_░lŽ┬Ą─Įyę╗ĪŻė╔ė┌UMLšZ┴x╩Ūś╦£╩╗»Ą─Ż¼Č°ŪęūŅ║¾Ą──┐ś╦┤·┤aė╔ŽĄĮyūįäė╔·│╔Ż¼▀@Š═Ž¹│²┴╦ė╔ė┌įOėŗ╚╦åTų«ķgŠÄ│╠’LĖ±▓╗═¼Č°įņ│╔Ą─┤·┤aĄ─▓╗▀Bž×ĪŻ

ė╔ė┌ų¦│ųSystemCĄ─UML╝▄śŗ╩Ū─┐Ū░EDAŅIė“▌^ą┬Ą─╝╝ągŻ¼Ųõ╣”─▄▀Ćį┌▓╗öÓĄ─öUš╣║═蹊┐ųąĪŻ─┐Ū░Ż¼Ę©ć°INRIA╣½╦ŠĄ─ķ_░ląĪĮM░l▒Ē┴╦└¹ė├ą“┴ąłDĄ╚▒Ē¼F▓óąą╝░īŹĢr╠žąįĄ─UMLöUš╣ś╦£╩“MARTE”Ż╗▒╚└¹ĢrKatholieke Universiteit Leuven╣½╦Šę▓╠ß│÷┴╦─▄ē“▒Ē¼FSoCė▓╝■ąį─▄ę¬Ū¾Ą─öUš╣ś╦£╩“SysML”Ż╗ęŌĘ©░ļī¦¾wät£╩éõ▀Mę╗▓ĮīŹ¼Fė╔SystemC│╠ą“ĄĮUMLĄ──µŽ“▐DōQ╣”─▄ĪŻ▀@ą®╣żū„Č╝īó▀Mę╗▓ĮöU┤¾UMLī”SoCĄ─Į©─Ż─▄┴”Ż¼╩╣│ķŽ¾Į©─Żį┌ąŠŲ¼įOėŗųąæ¬ė├Ė³╝ėÅVĘ║ĪŻ

4 īė┤╬╗»Ą─ĘųĮMģfū„╣▄└ĒĘĮĘ©

UMLĮ©─Żį┌SoCįOėŗ┴„│╠ųąĄ─æ¬ė├Ż¼ėąą¦╠ßĖ▀┴╦EDA╣ż│╠ųą▄øė▓╝■Ą─įOėŗą¦┬╩ĪŻ╚╗Č°Ż¼¼Fį┌Ą─EDA╣ż│╠ī”Å═ļsŽĄĮyĄ─įOėŗ╩Ū═©▀^īŻśIĘų╣żŻ©╚ń╣”─▄äØĘųĪó─ŻēKįOėŗĪóĘ┬šµ£yįćĪó░µłDęÄäØĪóĘŌčb▓╝ŠĆĄ╚Ż®║¾ą╬│╔ČÓéĆąĪĮM╣▓═¼ģfū„═Ļ│╔Ą─ĪŻ×ķ┴╦ģfš{ČÓĮMų«ķgĄ─Ęų╣żŻ¼┤_▒ŻąŠŲ¼Ė„éĆ─ŻēKį┌ČÓ╚╦įOėŗŽ┬Ą─╝µ╚▌ąį║═┘|┴┐ĘĆČ©ąįŻ¼╚╦éā═©│Ż▓╔ė├īė┤╬╗»Ą─ĘųĮMģfū„╣▄└ĒĘĮĘ©▀MąąÅ═ļsŽĄĮyĄ─įOėŗ╣▄└ĒĪŻ▀@ĘNīė┤╬╗»Ą─ĘųĮMģfū„╣▄└ĒĘĮĘ©ų„ę¬░³└©ęįŽ┬4éĆĘĮ├µŻ║

(1)╣ż│╠ųąąŠŲ¼ķ_░l╚╦åTīŹąąĘų╝ēÖÓŽ▐┐žųŲĪŻ╣ż│╠╣▄└Ēš▀┐╔ęįįOų├š¹éĆ╣ż│╠Ż¼▓ķ┐┤Ė„ąĪĮMĄ─▀MČ╚║═ICįOėŗ┴„│╠Ė„éĆŁh╣ØĄ─ł╠ąąŪķørŻ¼ī”öĄō■Äņėą╚½ÖÓĄ─ūxīæÖÓ└¹ĪŻČ°ąĪĮM╣▄└ĒåT×ķĮMā╚├┐éĆ│╔åT▀MąąŠ▀¾wĘų╣żŻ¼Ęų┼õ┘Yį┤Ż©╚ńįOėŗ╣żŠ▀Ż¼öĄō■╬─╝■Ą╚Ż®Ż¼žōž¤▒ŠĮM║═Ųõ╦¹ąĪĮMų«ķgĄ─▀MČ╚ģfš{ĪŻ

(2)ČÓĮMų«ķgĄ─═©ą┼ŲĮ┼_▓╔ė├īŹĢrĄ─╣ż│╠ą┼Žó╣▄└ĒÖCųŲĪŻ╣▄└ĒåTŽĒėąąŠŲ¼░µ▒Š║═ą▐Ė─ĘĮ░ĖĄ─░l▓╝ÖÓŻ¼╠Ä└Ēė╔Ųõ╦¹│╔åT╠ßĮ╗Ą─┘Yį┤╔ĻšłŻ¼įOėŗĘĮ░ĖĄ╚Ż¼Č°Ųõ╦¹│╔åT┐╔ęįČ©ųŲūį╝║Ą─ą┼Žó╠Ä└ĒĘĮ╩ĮŻ¼ęį▒ŃūŅ┐ņĄž½@Ą├╣ż│╠ą┼ŽóĪŻ

(3)▓╔ė├ĘųīėĄ─╬─╝■ŽĄĮy┤µĘ┼╣ż│╠ą┼ŽóŻ©░³└©ąŠŲ¼įOėŗöĄō■Īó▄øė▓╝■┘Yį┤öĄō■Īó│╔åTą┼ŽóĄ╚Ż®Ż¼▓óŪę×ķ├┐éĆķ_░ląĪĮM╠ß╣®¬Ü┴óĄ─╣żū„ģ^║═┘Yį┤ÄņŻ¼╩╣įOėŗ╚╦åTį┌ūį╝║Ą─╣żū„─┐õøŽ┬╣żū„ĪŻ╬─╝■ŽĄĮy└’▀ĆŅAČ©┴x┴╦ę╗ŽĄ┴ą╣”─▄öUš╣ęÄätŻ¼įOėŗ╚╦åT┐╔ęį░┤šš▀@ą®ęÄätī”ūį╝║Ą─╣żū„ģ^▀MąąąĶŪ¾įOėŗŻ¼└²╚ńą▐Ė─ūė─┐õøĖ±╩ĮŻ¼äōĮ©ą┼Žó░l▓╝ą╬╩ĮŻ¼ūįČ©┴xEDA╣żŠ▀Ą╚ĪŻ

(4)ī”ė┌┘Yį┤ÄņŻ¼░³└©ąŠŲ¼Ą─öĄō■ą┼ŽóÄņĪó╣ż│╠╚╦åTĘų╣żą┼ŽóÄņĪóĮ©─Ż╣żŠ▀ÄņŻ©╚ńroseŽĄ┴ąĄ─UMLĮ©─Ż▄ø╝■Ż®ĪóļŖ┬ĘįOėŗ╣żŠ▀ÄņŻ©╚ńCadenceŽĄ┴ą╣żŠ▀▄ø╝■Ż®Īóį¬╝■ą┼ŽóÄņĄ╚Ż¼īŹąąĘų╝ē╣▓ŽĒ║═╣▄└ĒĪŻį╩įSČÓéĆEDA╣ż│╠▀BĮėĄĮ─│ą®╣▓═¼Ą─┘Yį┤ÄņŻ¼Č°╣ż│╠ā╚▓┐│╔åTī”┘Yį┤ÄņĄ─▀BĮėĘČć·║═╩╣ė├ÖÓŽ▐Ż¼ė╔╣▄└ĒåTĖ∙ō■│╔åTĄ─Ęų╣żÖÓŽ▐ĮoėĶĘų┼õĪŻ

▀@ĘNīė┤╬╗»Ą─ĘųĮMģfū„╣▄└ĒĘĮĘ©╩╣įOėŗ╚╦åTų«ķgÖÓŽ▐├„┤_Ż¼╗ź▓╗Ė╔ö_Ż¼╠ßĖ▀┴╦ĒŚ─┐ķ_░lĄ─░▓╚½ąįĪŻŲõųąīŹĢrĄ─ą┼Žó╣▄└Ē╝ėÅŖ┴╦ĘųĮM│╔åTų«ķgĄ─ģfū„Ż¼ĘųīėĄ─╬─╝■┤µĘ┼ŽĄĮy╩╣╣ż│╠öĄō■Ė³ęūė┌▓ķįā║═╩╣ė├Ż¼┘Yį┤ÄņĄ─▀BĮė┐žųŲ║═╣▓ŽĒ╠ßĖ▀┴╦┘Yį┤Ą─└¹ė├┬╩║═╩╣ė├Ą─░▓╚½ąįĪŻ«öŪ░Ą─įSČÓEDA╣½╦ŠŻ©└²╚ńCadenceĪóSynopsys╣½╦ŠĄ╚Ż®Č╝═Ų│÷┴╦╗∙ė┌įōĘĮĘ©Ą─ĘųĮMģfū„╣▄└Ē▄ø╝■Ż©└²╚ńCadenceĄ─Team Design Manager6]Ą╚Ż®ĪŻę╗ą®EDAīŹ“×╩ę║═EDAŲĮ┼_Ą─Į©įOę▓ķ_╩╝╩╣ė├īė┤╬╗»Ą─╣▄└ĒĘĮĘ©Ż¼ęį╠ßĖ▀łFĻĀĄ─┐Ųčą║═ķ_░lą¦┬╩ĪŻ

─┐Ū░Ż¼īė┤╬╗»Ą─╣▄└ĒĘĮĘ©ų„ę¬▀mė├ė┌╩╣ė├═¼ę╗╣½╦ŠĄ─EDA╣żŠ▀Ą─ķ_░lłFĻĀĪŻČ°į┌┤¾ęÄ─ŻĄ─ąŠŲ¼įOėŗ┴„│╠ųąŻ¼įOėŗ╚╦åTėą┐╔─▄╗ņ║Ž╩╣ė├▓╗═¼╣½╦ŠŻ©└²╚ńCadenceĪóSynopsys║═Mentor Graphics╣½╦ŠŻ®Ą─EDA╣żŠ▀ĪŻ▀@ą®╣żŠ▀Ą─Įė┐┌ś╦£╩▓╗ę╗Č©ŽÓ═¼Ż¼╦∙ęįė├ę╗ĘNĘųĮM╣▄└Ē▄ø╝■ųąĄ─īė┤╬╗»╣▄└ĒĘĮĘ©ī”┐ń╣½╦ŠĄ─╣żŠ▀▀Mąą╣▄└Ē▀Ć┤µį┌ę╗Č©Ą─└¦ļyĪŻę“┤╦Ż¼╬ęéāīó▀@ĘNīė┤╬╗»Ą─╣▄└ĒĘĮĘ©┼cUMLĮY║ŽŻ¼╩╣ė├UML├Ķ╩÷ĘųĮMģfū„īė┤╬╗»ÖCśŗ║═EDA╣żŠ▀ų«ķgĄ─š{ė├Ż¼═¼Ģr└¹ė├UMLĄ─šZ┴xĄ─Įyę╗ąį┐╔ęį╔·│╔ę╗ų┬Ą─ś╦£╩Ż¼╗“į┌╬─╝■ų«ķg▀Mąąś╦£╩▐DōQŻ¼ęįĮŌøQ▓╗═¼╣żŠ▀Ą─ģfū„å¢Ņ}ĪŻ

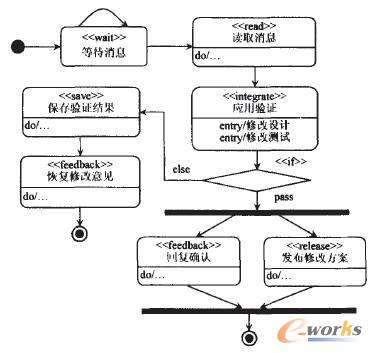

Ķbė┌UML╩Ūė├└²łDĪóĮYśŗłDĪó╗ŅäėłDĄ╚▀Mąą▒Ē╩ŠĄ─Ż¼▓╗Ą½─▄ē“├Ķ╩÷įOėŗ╚╦åTĄ─ÖÓŽ▐╣▄└Ē║═┘Yį┤Ęų┼õŻ¼▀Ć┐╔ęį├Ķ╩÷īė┤╬╗»įOėŗ╣▄└ĒųąĄ─▓╗═¼╣żŠ▀Įė┐┌ĪóįOėŗ▀^│╠ųąĄ─ą┼Žó╠Ä└ĒĄ╚å¢Ņ}ĪŻ╚ńłD5╦∙╩ŠŻ¼▓╔ė├UMLüĒ├Ķ╩÷╣▄└ĒåT▀Mąąą┼Žó╠Ä└Ē▀^│╠Ą─╗ŅäėłDĪŻ«öąŠŲ¼įOėŗ▀^│╠ųąėą─│éĆ─ŻēKąĶꬹ▐Ė─ĢrŻ¼╣▄└ĒåT═©│ŻĢ■╩šĄĮķ_░l╚╦åT╠ßĮ╗Ą─įOėŗą▐Ė─ĘĮ░ĖŻ¼╚╗║¾īóŲõæ¬ė├ĄĮš¹¾wįOėŗ▀MąąŠC║ŽĘ┬šµĪó£yįćĄ╚ę╗ŽĄ┴ą“×ūCŻ¼╚¶ą▐Ė─ĘĮ░Ė▓╗┐╔ąąŻ¼╣▄└ĒåTīóŽ“╠ßĮ╗š▀░l╦═“×ūCĮY╣¹║═ą▐Ė─Į©ūhĄ╚ą┼ŽóŻ¼╚¶ą▐Ė─ĘĮ░Ė┐╔ąąŻ¼╣▄└ĒåTīóŽ“╠ßĮ╗š▀░l╦═┤_šJą┼ŽóŻ¼═¼ĢrŽ“╣ż│╠ā╚Ųõ╦¹ąĪĮM░l▓╝įōą▐Ė─ĘĮ░ĖŻ¼╩╣Ė„ąĪĮM░┤ššĘĮ░ĖĖ³ą┬Ė„ūįžōž¤Ą─ąŠŲ¼▓┐ĘųĪŻŲõųąŻ¼ĀŅæBłDųą“do/…”šZŠõ╩Ū╣▄└ĒåTĖ∙ō■╣ż│╠ąĶ꬯¼ūįČ©┴xŠ▀¾wł╠ąąā╚╚▌Ż¼└²╚ńūųĘ¹┤«▐DōQĪóöĄō■ÄņūxīæĪó╣żŠ▀Ą─š{ė├ĪóĮė┐┌ś╦£╩▐DōQĄ╚ĪŻė╔ė┌UML┐╔ęį▓╔ė├ś╦£╩╗»Ą──Żą═║═┤·┤aüĒ▐DōQ▓╗═¼Ą─╣żŠ▀Ą─╬─╝■ś╦£╩Ż¼╩╣SoCįOėŗĄ─Ė„Ęų╣żąĪĮMī”▓╗═¼╣½╦ŠĄ─EDA╣żŠ▀š{ė├ūāĄ├Įyę╗Ż¼ėą└¹ė┌┐žųŲąŠŲ¼─ŻēKĄ─┘|┴┐Ż¼Å─Č°┤_▒ŻsocąŠŲ¼Ą─įOėŗą¦┬╩║═┘|┴┐ĪŻ

łD5 Ž¹Žó╠Ä└Ē╗ŅäėłD

5 ĮYšZ

ĮY║ŽUMLĮ©─ŻĄ─SoCįOėŗĘĮĘ©║═īė┤╬╗»Ą─ĘųĮM╣▄└ĒĘĮĘ©ėąą¦ĄžĮŌøQ┴╦«öŪ░ąŠŲ¼įOėŗĢrŽ▐┐sČ╠ĪóįOėŗĘų╣ż▓╗öÓÅ═ļs╗»Č°Ä¦üĒĘNĘNå¢Ņ}ĪŻUMLĮ©─Ż┼cSoCįOėŗĄ─ĮY║ŽŻ¼īŹ¼F┴╦ąŠŲ¼Ą─ŽĄĮy╝ēįOėŗĪŻų¦│ųSystemCĄ─UML╝▄śŗį┌▀@ĘNą┬ą═įOėŗ┴„│╠ųąĄ─╩╣ė├Ż¼┐╔ęįėąą¦ŃĢĮėÅ─ė▓╝■ĘųļxĄĮ▀M╚ļRTL╝ēĄ─įOėŗ▀^│╠Ż¼ĮŌøQ┴╦ė▓╝■▓┐Ęųį┌RTL╝ēĄ─įOėŗ│ķŽ¾īė┤╬Ą═ĪóÕeš`Öz£y▓╗╝░ĢrĄ─└¦ļyŻ¼╠ßĖ▀┴╦ąŠŲ¼Ą─ķ_░lą¦┬╩ĪŻČ°īė┤╬╗»Ą─ĘųĮMģfū„╣▄└ĒĘĮĘ©─▄ē“ī”ėąą¦ģfš{SoCįOėŗ┴„│╠ųąČÓéĆįOėŗąĪĮMĄ─Å═ļsĘų╣ż┼cģfū„Ż¼╩╣ąŠŲ¼Ė„─ŻēKį┌ČÓ╚╦ķ_░lĄ─▀^│╠ųą╩╝ĮK╝µ╚▌ę╗ų┬Ż¼▀@ĘN╣▄└ĒĘĮĘ©┼cUMLĄ─ĮY║Ž▀Ćėą└¹ė┌ā×╗»ĘųĮMģfū„Ż¼ĮŌøQ▓╗═¼ś╦£╩Ą─EDA╣żŠ▀ų«ķgĄ─ģfū„å¢Ņ}ĪŻ

║╦ą─ĻPūóŻ║═ž▓ĮERPŽĄĮyŲĮ┼_╩ŪĖ▓╔w┴╦▒ŖČÓĄ─śIäšŅIė“ĪóąąśIæ¬ė├Ż¼╠N║Ł┴╦žSĖ╗Ą─ERP╣▄└Ē╦╝ŽļŻ¼╝»│╔┴╦ERP▄ø╝■śIäš╣▄└Ē└Ē─ŅŻ¼╣”─▄╔µ╝░╣®æ¬µ£Īó│╔▒ŠĪóųŲįņĪóCRMĪóHRĄ╚▒ŖČÓśIäšŅIė“Ą─╣▄└ĒŻ¼╚½├µ║Ł╔w┴╦Ų¾śIĻPūóERP╣▄└ĒŽĄĮyĄ─║╦ą─ŅIė“Ż¼╩Ū▒ŖČÓųąąĪŲ¾śIą┼Žó╗»Į©įO╩ū▀xĄ─ERP╣▄└Ē▄ø╝■ą┼┘ćŲĘ┼ŲĪŻ

▐D▌dšłūó├„│÷╠ÄŻ║═ž▓ĮERP┘YėŹŠWhttp://www.guhuozai8.cn/

▒Š╬─ś╦Ņ}Ż║EDA╣ż│╠Į©─Ż╝░Ųõ╣▄└ĒĘĮʩ蹊┐