▒Š╬─ėæšō▓╗═¼Ą─┤µ╚Ī╝╝ągī”ė┌DRAMį┌▀MąąīŹ¾wįOėŗĢr╦∙░l╔·Ą─Ė─ūāŻ¼ė╚Ųõ╩ŪųĖė╔1ļŖŠ¦¾w+1ļŖ╚▌Ų„ĮM│╔Ą─ā”┤µå╬į¬——DRAMĄ─ūŅąĪėøæøå╬╬╗…

▓╗═¼Ą─┤µ╚Ī╝╝ągī”ė┌äėæBļSÖC┤µ╚Ī┤µā”Ų„(DRAM)į┌▀MąąīŹ¾wįOėŗĢrīó░l╔·╩▓├┤Ė─ūāŻ┐«öäėæBļSÖC┤µ╚Ī┤µā”Ų„(DRAM)ųąĄ─ā”┤µå╬į¬(storage cell)╝ė╔Ž┐žųŲČ╦³cęį╝░öĄō■Č╦³c║¾Ż¼Š═▒╗ĘQ×ķ1T1C DRAMå╬į¬;ŲõųąŻ¼┐žųŲČ╦³cę▓Š═╩ŪūųĮMŠĆ(WL)Ż¼ė├ė┌é„▀f╬╗ųĘėŹ╠¢Ż¼öĄō■Č╦³cę▓Š═╩Ū╬╗į¬ŠĆ(BL)Ż¼ė├ė┌é„▀föĄō■ųĄĪŻ

Ļć┴ąĮYśŗĄ─▓Ņ«É

ķLŲ┌ęįüĒŻ¼ī”ė┌DRAMå╬į¬Ļć┴ąų«ųąĄ─╬╗į¬ŠĆ╩Ū╩╣ė├▓Ņäėī”(differential pair)Ą─śė╩ĮüĒ┼õų├Ż¼ė┌╩Ū╬╗į¬ŠĆŠ═▒╗ģ^Ęų│╔“+BL”ęį╝░“-BL”;▒Š╬─īó▀@śėĄ─Ļć┴ąĮYśŗ├³├¹×ķ▓Ņäė╩Įā”┤µĻć┴ą(Differential Storage Array)Ż¼░³║¼▀@ĘNĻć┴ąĮYśŗĄ─DRAMąŠŲ¼Š═├¹×ķ▓Ņäė╩ĮDRAMąŠŲ¼ĪŻŽÓī”ė┌▓Ņäė╩Įā”┤µĻć┴ąŻ¼ą┬Ą─┤µ╚Ī╝╝ąg┐╔╩╣ė├å╬Č╦Ą─śė╩ĮüĒ┼õų├Ż¼ė┌╩Ū╬╗į¬ŠĆŠ═╩Ū“BL”;▒Š╬─īó▀@śėĄ─Ļć┴ąĮYśŗ├³├¹×ķå╬Č╦╩Įā”┤µĻć┴ąŻ¼░³║¼▀@ĘNĻć┴ąĮYśŗĄ─DRAMąŠŲ¼Š═├¹×ķå╬Č╦╩ĮDRAMąŠŲ¼ĪŻ

į┌łD1ū¾╔ŽĘĮ│╩¼Fā”┤µå╬į¬Ą─ļŖ┬ĘłDŻ¼▀@Š═╩Ū1T1C DRAMąŠŲ¼Ą─ėøæøå╬╬╗ĪŻį┌łD1ųąŻ¼×ķ┴╦ŪÕ│■▒╚▌^▓Ņäė╩Įā”┤µĻć┴ą┼cå╬Č╦╩Įā”┤µĻć┴ąų«ķgĄ─▓Ņ«ÉŻ¼╠žäeīó╔Ž░ļ▓┐└LųŲ│╔▓Ņäė╩Įā”┤µĻć┴ąŻ¼ėųīóŽ┬░ļ▓┐└LųŲ│╔å╬Č╦╩Įā”┤µĻć┴ąĪŻ▀@śė▒Š╩Ūīó╬╗ųĘ┐šķgįOČ©×ķ4Ż¼ŲõųąŻ¼▀BĮėČ©ųĘļŖ┬ĘĄ─ī¦ŠĆ╝┤╩ŪWL0ų┴WL3ĪŻ▀BĮėöĄō■é„▌öļŖ┬ĘĄ─ī¦ŠĆī”ė┌▓Ņäė╩Įā”┤µĻć┴ąĄ─įOėŗ╩ŪBL00 (+BL)ęį╝░BL10 (-BL)Ż¼╦³Ą─öĄō■īÆČ╚╩Ū2Ż¼▓óŪę▒ž×ķ┼╝öĄŻ¼Ą½╩Ūå╬Č╦╩Įā”┤µĻć┴ąŠ═ų╣ė┌BL0Ż¼╦³Ą─öĄō■īÆČ╚╩Ū1Ż¼┐╔×ķŲµöĄĪŻ▓Ņäė╩Įā”┤µĻć┴ąėąÅ═ļsĄ─ī¦ŠĆ▀BĮėĘĮ╩ĮŻ¼▓óŪę▒žĒÜĮ╗Õe▀BĮė╬╗ųĘŠĆŻ¼▀@ėų▒╗ĘQ×ķŲµ┼╝▀BŠĆŻ¼Ž±─ŪBL00Š═╩Ū┼õ║ŽWL0ęį╝░WL2üĒ┤µ╚ĪöĄō■ĪŻ

Å─łD 1┐╔ŪÕ│■┐┤│÷å╬Č╦╩Įā”┤µĻć┴ąŽÓī”ė┌▓Ņäė╩Įā”┤µĻć┴ąĄ─ā×ä▌Ż¼─ŪŠ═╩Ū║åå╬└■┬õĄž▀BĮė╚½▓┐Ą─ī¦ŠĆŻ¼▀@į┌▓╝ŠųĄ─Ģr║“┐╔£p▌p└@ŠĆĄ─╣żū„┴┐ęį╝░║å╗»ā”┤µå╬į¬Ą─┼┼┴ą;į┌īŹ¾wļŖ┬Ęųą┐╔╚ź│²▓Ņäėī”Ą─ļŖē║╗źŽÓė░Ēæ┴Ēę╗ŽÓī”Ą─ā”┤µå╬į¬Ż¼ę▓Š═╩Ūį┌▀Mąą┤µ╚ĪĢrĢ■╗źŽÓė░Ēæ─Ūą®į┌ā”┤µå╬į¬ų«ā╚Ą─ļŖē║ųĄŻ¼▀@įŁę“Üwė┌ļŖŠ¦¾wĄ─ą╣┬®ļŖ┴„ĪŻ

łD1Ż║▓Ņäė╩Įā”┤µĻć┴ą┼cå╬Č╦╩Įā”┤µĻć┴ąĄ─▓Ņ«É

ęÄĖ±įOėŗĄ─▓Ņ«É

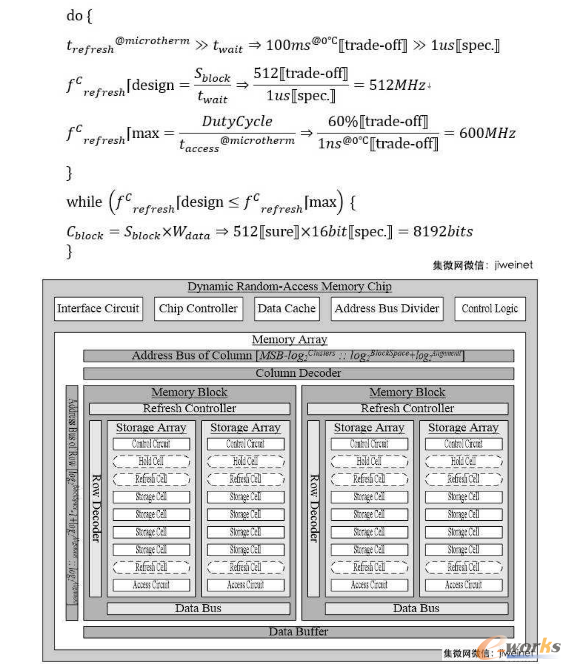

į┌ęÄĖ±įOėŗ╔ŽŻ¼DRAMąŠŲ¼Ģ■┼õų├įSČÓā”┤µĻć┴ąŻ¼▒Š╬─īó▀@ą®ā”┤µĻć┴ą╦∙ą╬│╔Ą─▓╝Šųģ^ė“├³├¹×ķ┤µā”Ų„Ļć┴ąŻ¼▓óŪę▀@ę╗┤µā”Ų„Ļć┴ąėų┐╔ĘųĖŅ│÷įSČÓ┤µā”Ų„ģ^ēKŻ¼▀Ć┐╔Š█╝»▀@ą®┤µā”Ų„ģ^ēK│╔ę╗ģ^ēK┤ž(Block Cluster)ĪŻĻPė┌▒Š╬─╦∙╠ß│÷Ą─DRAMąŠŲ¼╩ŪęįłD2üĒ│╩¼F╦³Ą─ā╚▓┐╝▄śŗŻ¼▀@ą®┤µā”Ų„ģ^ēK┼õų├ŽÓ═¼Ą─Č©ųĘ┐šķgŻ¼║åĘQģ^ēK┐šķgŻ¼▀@ę╗ģ^ēK┐šķg░³║¼ČÓéĆ┼cöĄō■īÆČ╚ŽÓĄ╚Ą─å╬Č╦╩Įā”┤µĻć┴ąŻ¼╗“╩Ū░³║¼ČÓéĆ┼c░ļöĄöĄō■īÆČ╚ŽÓĄ╚Ą─▓Ņäė╩Įā”┤µĻć┴ąĪŻį┌łDųąėąś╦ėø▒Ż│ųå╬į¬(Hold Cell)ęį╝░Ė³ą┬å╬į¬(Refresh Cell)Ż¼▀@ąĶę¬Ęųäe┼õ║Žų„äė▒Ż│ų(Active Hold)ęį╝░ų„äėĖ³ą┬(Active Refresh)Ą─╣”─▄ĪŻį┌┤µā”Ų„ģ^ēKų«ā╚░³║¼Ė³ą┬┐žųŲŲ„ęį╝░┴ąĮŌ┤aŲ„╝┤┐╔Įøė╔ŲĮąą╝╝ągüĒł╠ąąŠų▓┐Ė³ą┬ū„śIĪŻ

ėąįSČÓę“╦ž┐╔øQČ©ģ^ēK┐šķg(Sblock)Ż¼Ž±╩Ūł╠ąąĖ³ą┬ū„śIĄ─Ģr├}Ņl┬╩ĪóĄ╚┤²Ė³ą┬ū„śI═Ļ│╔Ą─ĢrķgĪół╠ąąĖ³ą┬ū„śIĄ─ķgĖ¶Ģrķgęį╝░ł╠ąą┤µ╚Īū„śIĄ─Ģrķg;ęį╔Ž▀@ą®ę“╦žĘųäe║åĘQ×ķĖ³ą┬Ģr├}Ņl┬╩(fCrefresh)ĪóĄ╚┤²Ģrķg(t_wait)ĪóĖ³ą┬Ģrķg(t_refresh)ęį╝░┤µ╚ĪĢrķg(t_access)ĪŻģ^ēK┐šķg┼cöĄō■īÆČ╚(W_data)Ą─│╦ĘeŠ═╩Ū┤µā”Ų„ģ^ēK╦∙║¼ėąĄ─╬╗į¬öĄŻ¼├¹×ķģ^ēK╚▌┴┐(C_block)ĪŻ▀@ą®ę“╦žų«ķgĄ─ĻPŽĄ┐╔ė╔ęįŽ┬Ą─öĄīWĘĮ│╠╩ĮüĒ▒Ē▀_Ż¼▓óļSĖĮĘČ└²į┌║¾Ż║

łD2Ż║DRAMąŠŲ¼ā╚▓┐╝▄śŗ

īŹ¾wĮYśŗĄ─▓Ņ«É

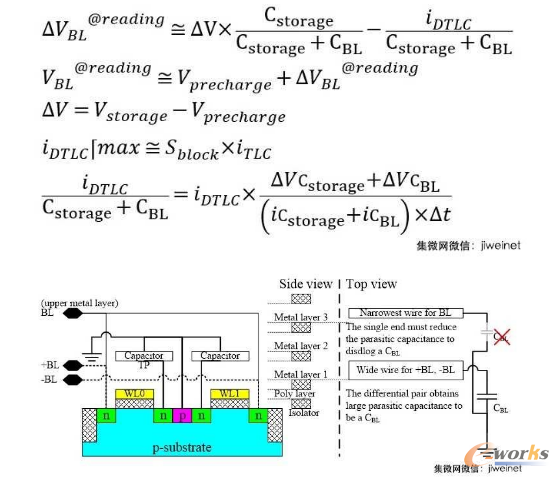

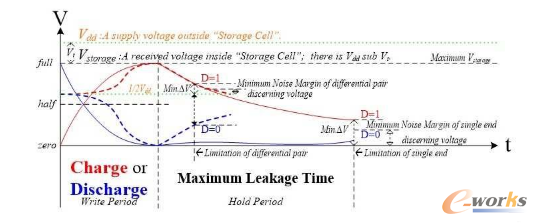

į┌īŹ¾wĮYśŗųąŻ¼å╬ę╗ā”┤µĻć┴ą╔Ž▀BĮė╦∙ėąā”┤µå╬į¬Ą─å╬ę╗╬╗į¬ŠĆŻ¼įōĮī┘ī¦ŠĆĄ─ķLČ╚ęį╝░╝─╔·ļŖ╚▌Ģ■Ž▐ųŲģ^ēK┐šķgĄ─ūŅ┤¾ųĄŻ¼▀@ę¬Å─ā”┤µĻć┴ąĄ─▓╝Šųęį╝░ā”┤µå╬į¬Ą─╠žąįüĒĘų╬÷▀@ą®ę“╦žĪŻłD3│╩¼Fėąę╗īŹ¾wĮYśŗüĒ╩ŠęŌĮī┘ī¦ŠĆį┌Š¦┴Ż╔ŽĄ─▓╝ŠųŻ¼ŲõųąŻ¼é╚ęĢłD│╩¼F▓Ņäė╩Įā”┤µĻć┴ąīó─Ūą®┼c+BLęį╝░-BL▀BĮėĄ─Įī┘ī¦ŠĆĘ┼ų├į┌▒╚▌^Ž┬├µĄ─Įī┘īėŻ¼Ž±╩ŪĄ┌ę╗Įī┘īėŻ¼į┌łDųąęį┤ų³cŠĆ╩ŠęŌ;å╬Č╦╩Įā”┤µĻć┴ąĘ┤Č°īó─Ūą®┼cBL▀BĮėĄ─Įī┘ī¦ŠĆĘ┼ų├į┌▒╚▌^╔Ž├µĄ─Įī┘īėŻ¼Ž±╩ŪĄ┌╚²Įī┘īėŻ¼į┌łDųąęį╝ÜīŹŠĆ╩ŠęŌĪŻĒöęĢłD│╩¼F▓Ņäė╩Įā”┤µĻć┴ąĢ■╝ėīÆĮī┘ī¦ŠĆüĒį÷╝ė╝─╔·ļŖ╚▌;å╬Č╦╩Įā”┤µĻć┴ąĘ┤Č°ę¬╩╣ė├ūŅąĪĄ─ŠĆīÆüĒ╚ź│²╝─╔·ļŖ╚▌ĪŻ

ęįŽ┬šłī”ššłD3Ż¼«öWL0╗“WL1╩╣Ą├ļŖŠ¦¾wī¦═©ų«║¾Ż¼┼cŲõ▀BĮėĄ─ļŖ╚▌Ų„Š═Ģ■Ž“BL╗“+BL╗“-BLĘ┼ļŖŻ¼╬╗į¬ŠĆĄ─ļŖ┴„Įø▀^ę╗Č╬Įī┘ī¦ŠĆų«║¾▀BĮėų┴öĄō■“īäėŲ„ęį╝░öĄō■Įė╩šŲ„ĪŻ─Ūą®╝─╔·į┌Įī┘ī¦ŠĆĄ─╚½▓┐ļŖ╚▌į┌łDųą▒╗ś╦ėø×ķ“C_BL”Ż¼▀@ļŖ╚▌┴┐ę▓ĻP┬ōė┌īŹ¼F╗žīæ╣”─▄Ą─ė▓¾wļŖ┬Ę;łDųąėąę╗£yįć³c(TP)ė├ė┌╠Į£yā”┤µå╬į¬Ą─ā”┤µĀŅæBŻ¼╦³Ą─ļŖē║ųĄ╝┤╩Ūā”┤µļŖē║(V_storage)ĪŻ«ö£yįć³cĄ─ļŖ║╔ųØuęŲų┴Įī┘ī¦ŠĆų«ĢrŻ¼£yįć³cĄ─ļŖē║ę▓Ģ■ųØuŽ┬ĮĄŻ¼│²┤╦ų«═ŌŻ¼─Ūą®┼c╬╗į¬ŠĆ▀BĮėĄ─ļŖŠ¦¾wĮįėąą╣┬®ļŖ┴„Ż¼╔§ų┴╩ŪöĄō■“īäėŲ„Ą─▌ö│÷Č╦Ż¼ę“┤╦Ż¼─Ūą®ęŲų┴Įī┘ī¦ŠĆĄ─ļŖ║╔ėųĢ■▒╗Ħū▀ĪŻ╚ń╣¹╠ßĖ▀C_BLĄ─ļŖ╚▌┴┐Š═─▄ē“£pŠÅļŖ║╔Å─Įī┘ī¦ŠĆ▒╗Ħū▀Ą─╦┘Č╚Ż¼╚╗Č°Ż¼Įī┘ī¦ŠĆąĶę¬Å─£yįć³c╚ĪĄ├Ė³ČÓĄ─ļŖ║╔üĒ└█ĘeūŃē“Ą─ļŖē║ųĄŻ¼╚ń┤╦▓┼─▄┼ąöÓöĄō■ųĄŻ¼┤╦═ŌĢ■į÷╝ėŅA│õļŖĄ─Ģrķg;▀@ę╗¼FŽ¾Ģ■į÷╝ėūx╚Īū„śIĄ─Ģrķgęį╝░╗žīæū„śIĄ─ĢrķgĪŻ╚ń╣¹C_BLĄ─ļŖ╚▌┴┐─▄ē“┌ģĮ³ė┌┴Ń╝┤┐╔┐sČ╠ŅA│õļŖĄ─ĢrķgŻ¼Ą½╩Ū─Ūą®ęŲų┴Įī┘ī¦ŠĆĄ─ļŖ║╔Š═Ģ■čĖ╦┘┴„╩¦Ż¼▓óŪę£yįć³cĄ─ļŖē║ųĄę▓Ģ■čĖ╦┘Üw┴Ń;▀@ę╗¼FŽ¾╚ń═¼░l╔·┴╦═╗▓©Č°ī¦ų┬öĄō■Įė╩šŲ„▓╗─▄┼ąöÓöĄō■ųĄŻ¼╚╗Č°Ż¼▀@ėą┐╔─▄Įøė╔į÷ÅŖöĄō■Įė╩šŲ„Ą─š¹¾wą¦─▄Č°ĮŌøQĪŻ▀@ę╗╝─╔·ļŖ╚▌ī”ė┌▓Ņäė╩Įā”┤µĻć┴ąČ°čį╩ŪąĶę¬ūŃē“┤¾Ą─ļŖ╚▌┴┐üĒ┼ąöÓöĄō■ųĄŻ¼ī”ė┌å╬Č╦╩Įā”┤µĻć┴ąĘ┤Č°Ų┌═¹Ą├ĄĮūŅąĪĄ─ļŖ╚▌┴┐Ż¼Ę±ät▓╗ų╣ąĶę¬Ė³ķLĄ─╗žīæĢrķgüĒ╗ųÅ═ā”┤µĀŅæBŻ¼ę▓ėą┐╔─▄ąĶę¬Ė³┤¾Ą─ļŖ╚▌┴┐üĒŠS│ųš²į┌ūx╚Īų«ĢrĄ─öĄō■ųĄŻ¼╔§ų┴¤oĘ©┼ąöÓöĄō■ųĄĪŻ

ģ^ēK┐šķgĄ─ūŅ┤¾ųĄš²▒╚ė┌öĄō■Įė╩šŲ„Ą─š¹¾wą¦─▄Ż¼š²▒╚ė┌─Ūį┌ā”┤µå╬į¬ā╚▓┐Ą─ļŖ╚▌┴┐(C_storage)Ż¼Ę┤▒╚ė┌Įī┘ī¦ŠĆĄ─╝─╔·ļŖ╚▌Ż¼Ę┤▒╚ė┌Įī┘ī¦ŠĆĄ─┐éūĶ┐╣ųĄŻ¼Ę┤▒╚ė┌ļŖ┴„┬ĘÅĮų«ųąĄ─äėæB┐éą╣┬®ļŖ┴„(i_DTLC)Ż¼▀@║ŁęŌ╝┤╩Ū├┐«öėąę╗ā”┤µĻć┴ąš²į┌┤µ╚Īų«ĢrŠ═Ģ■Ė∙ō■Ė„ā”┤µå╬į¬Ą─ā”┤µļŖē║ųĄČ°äėæBĄžūā╗»ĪŻĮøė╔ļŖ╚▌Ų„Ą─ļŖ║╔Ęųē║Č©┬╔Č°─▄╦Ń│÷š²į┌ūx╚ĪöĄō■ų«Ģr─Ūį┌╬╗į¬ŠĆ╔ŽĄ─ļŖē║ųĄŻ¼ęÓ╝┤“V_BL(@reading)”Ż¼öĄīWĘĮ│╠╩Į╚ń║¾Ż¼ŲõųąŻ¼“V_BL(@reading)”╩Ū─Ūį┌╬╗į¬ŠĆ╔ŽĄ─▓Ņ«ÉļŖē║ųĄŻ¼“V_precharge”╩ŪŅA│õļŖĄ─ļŖē║ųĄŻ¼▀@ļŖē║ųĄį┌▓Ņäė╩Įā”┤µĻć┴ą╩Ū1/2V_ddŻ¼į┌å╬Č╦╩Įā”┤µĻć┴ą╩Ū0Ż║

łD3Ż║ā╚║¼2ĘNā”┤µå╬į¬Ą─īŹ¾wĮYśŗ▓Ņ«É

ā”┤µļŖē║Ą─▓Ņ«É

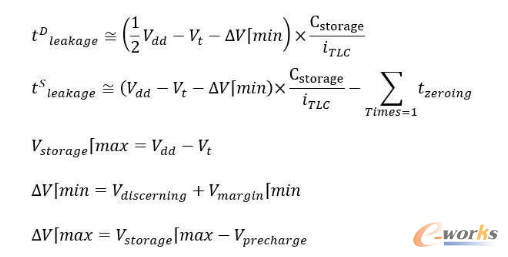

į┌▀M╚ļ▀@Č╬Ą─ų„Ņ}ų«Ū░ꬎ╚ŪÕ│■Č©┴xęįŽ┬Ą─├¹į~Ż║“ļŖį┤ļŖē║(V_dd)”╩Ū╬╗ė┌ā”┤µå╬į¬ų«═ŌĄ─╣®æ¬ļŖē║Ż¼ę▓Š═╩ŪŽ“ų°öĄūų▀ē▌ŗļŖ┬ĘČ°╣®æ¬š²ļŖē║Ą─ļŖį┤;“ā”┤µļŖē║(V_storage)”╩Ū╬╗ė┌ā”┤µå╬į¬ų«ā╚ė├ė┌Įė╩šļŖē║ųĄ▓óŪę▒M┴┐ŠS│ųŲõ╦∙ī”æ¬Ą─▀ē▌ŗ£╩╬╗üĒ╠ß╣®ūx╚ĪŲ┌ķgĄ─öĄō■ųĄ;“ĶbäeļŖē║(V_discerning)”╩ŪöĄō■Įė╩šŲ„į┌ūx╚ĪŲ┌ķg╗“Ė³ą┬Ų┌ķg─▄ē“ī”ūŅ╬óąĪĄ─ļŖē║ūā╗»Č°ĶbäeöĄō■ųĄĄ─śOŽ▐ųĄ;“ūŅąĪļsėŹ▀ģĮń(V_margin®@MIN)”╩ŪöĄō■Įė╩šŲ„į┌ūx╚ĪŲ┌ķg╗“Ė³ą┬Ų┌ķgā╚╩▄ĄĮĖ„ŅÉļsėŹĄ─Ė╔ö_Ģrę▓─▄ē“ĶbäeöĄō■ųĄĄ─ūŅąĪ▀ģĮńļŖē║ųĄŻ¼▀@ą®ļsėŹ░³║¼ļŖį┤ļsėŹęį╝░ŪąōQļsėŹ;“ūŅąĪ▓Ņ«ÉļŖē║(ΔV®@MIN))”Ą╚ė┌ĶbäeļŖē║╝ė╔ŽūŅąĪļsėŹ▀ģĮńŻ¼╩Ūį┌ūx╚ĪŲ┌ķg╗“Ė³ą┬Ų┌ķg─▄ē“į┌╩▄ĄĮļsėŹĖ╔ö_ų«Ģrę▓─▄▒╗öĄō■Įė╩šŲ„ĶbäeöĄō■ųĄĄ─ūŅąĪā”┤µļŖē║Ż¼▀@ļŖē║ę▓Ģ■ė░ĒæĖ³ą┬ĢrķgĄ─śOŽ▐ųĄĪŻ┴Ē═ŌŻ¼“å╬į¬ļŖē║(V_cell)”╩Ū╣Pš▀░l▒ĒėąĻPSRAMĄ─┤µ╚Ī╝╝ągĢr╦∙╠ß│÷Ą─ę╗ĘN╣®æ¬ļŖē║Ż¼▀@ė├═Š▓╗═¼ė┌ā”┤µļŖē║ĪŻ

łD4│╩¼F▓Ņäė╩Įā”┤µĻć┴ąęį╝░å╬Č╦╩Įā”┤µĻć┴ąĄ─ā”┤µļŖē║Ż¼▓óŪę═╗’@į┌å╬ę╗ā”┤µå╬į¬ų«ųąĄ─▓Ņ«ÉĪŻ×ķ┴╦║÷┬į▓╗═¼Ą─ā”┤µĻć┴ąį┌┤µ╚Ī╝╝ąg╔ŽĄ─▓Ņ«ÉŻ¼╦∙ęį▀@ļŖē║▓©ą╬łD╦∙ī”æ¬ĄĮĄ─ė▓¾wļŖ┬ĘŠ═╩Ūå╬ę╗ā”┤µå╬į¬ĪŻōQčįų«Ż¼▀@╩ŪįOČ©į┌ŽÓ═¼Ą─ųŲ│╠ģóöĄĪóļŖ╚▌┴┐ęį╝░ą╣┬®ļŖ┴„üĒ▒╚▌^ĻPė┌ā”┤µļŖē║Ą─▓Ņ«ÉĪŻ

ļŖŠ¦¾wĄ─ķlśOļŖē║(V_t)Ģ■╩╣Ą├ā”┤µļŖē║Ą═ė┌ļŖį┤ļŖē║Ż¼╚ń╣¹ųØuį÷╝ėļŖŠ¦¾wĄ─ķlśOļŖē║ät┐╔╩╣Ą├ā”┤µļŖē║ųØu┌ģĮ³ļŖį┤ļŖē║ĪŻ▓Ņäė╩Įā”┤µĻć┴ą×ķ┴╦╚ź│²ķlśOļŖē║Ż¼ė┌╩Ūį┌┤µ╚ĪŲ┌ķgų«ā╚Ģ■┴ŅūųĮMŠĆĄ─ļŖē║ųĄų┴╔┘ĄĮ▀_ļŖį┤ļŖē║╝ė╔ŽķlśOļŖē║Ż¼╩╣Ą├ūŅ┤¾Ą─ā”┤µļŖē║Ą╚ė┌ļŖį┤ļŖē║ĪŻå╬Č╦╩Įā”┤µĻć┴ą│²┴╦┐╔Įøė╔╔Ž╩÷Ą─į÷ē║ĘĮĘ©üĒ▀_ĄĮ═¼śėĄ─ą¦╣¹ų«═ŌŻ¼╔ą┐╔Įøė╔ČÓķlśOļŖē║Ą─ųŲ│╠╝╝ągüĒ╩╣ė├Ė▀ķlśOļŖē║Ą─ļŖŠ¦¾wŻ¼╚ń┤╦▀Ć─▄£pąĪą╣┬®ļŖ┴„ĪŻī”ė┌£pąĪą╣┬®ļŖ┴„Ą─ļŖ┬Ęę▓─▄╩╣ė├╚²┌ÕųŲ│╠(triple-well process)üĒįOėŗ┴ąĮŌ┤aŲ„Ą─▌ö│÷“īäėŲ„Ż¼╚ń┤╦╝┤┐╔┴ŅūųĮMŠĆęįžōļŖē║Įžų╣ļŖŠ¦¾wĪŻ

łD4Ą─ļŖē║▓©ą╬łD╩Ū│╩¼F╚ź│²ķlśOļŖē║Ą─ė░ĒæČ°ą╬│╔Ą─╣żū„ĀŅæBĪŻį┌īæ╚ļŲ┌ķgų«ā╚Ż¼▓Ņäė╩Įā”┤µĻć┴ąĄ─ā”┤µļŖē║Ģ■Ž╚ĄĮ▀_ŅA│õļŖĄ─ļŖē║ųĄŻ¼╚╗║¾ĄĮ▀_╦∙▒╗īæ╚ļĄ─ļŖē║ųĄ;╚╗Č°Ż¼å╬Č╦╩Įā”┤µĻć┴ąø]ėąŅA│õļŖĄ─ļŖē║ųĄĪŻį┌▒Ż│ųŲ┌ķgų«ā╚Ż¼▓Ņäė╩Įā”┤µĻć┴ąĄ─ā”┤µļŖē║Ģ■ųØu┌ģĮ³░ļ▒ČĄ─ļŖį┤ļŖē║ųĄ;╚╗Č°Ż¼å╬Č╦╩Įā”┤µĻć┴ą╩ŪųØu┌ģĮ³ūŅąĪĄ─ļŖē║ųĄŻ¼ęÓ╝┤ĮėĄžļŖē║ųĄĪŻė╔┤╦┐┤│÷å╬Č╦╩Įā”┤µĻć┴ąĄ─Ė³ą┬Ģrķg┤¾╝s╩Ū▓Ņäė╩Įā”┤µĻć┴ąĄ─Č■▒ČĪŻ

łD5╩Ū×ķ┴╦═╗’@▓Ņäė╩Įā”┤µĻć┴ą┼cå╬Č╦╩Įā”┤µĻć┴ąų«ķgĄ─ą¦ęµ▓Ņ«ÉŻ¼╦∙ęį▀@ļŖē║▓©ą╬łD│╩¼F╝ė╚ļķlśOļŖē║╦∙ą╬│╔Ą─ė░ĒæĪŻį┌īæ╚ļŲ┌ķgų«ā╚Ż¼ūŅ┤¾Ą─ā”┤µļŖē║ųĄĄ═ė┌ļŖį┤ļŖē║ųĄŻ¼▀@ė░Ēæ┴╦▓Ņäė╩Įā”┤µĻć┴ąĄ─ļŖē║ī”ĘQąįĪŻį┌▒Ż│ųŲ┌ķgų«ā╚Ż¼ī”ė┌▓Ņäė╩Įā”┤µĻć┴ąĄ─ā”┤µļŖē║Ż¼Ę┼ļŖŪ·ŠĆ▒╚│õļŖŪ·ŠĆĖ³┐ņĄĮ▀_░ļ▒ČĄ─ļŖį┤ļŖē║ųĄŻ¼╩╣Ą├Ė³ą┬Ģrķg▒╗Ų╚┐sČ╠ĪŻė╔┤╦┐┤│÷å╬Č╦╩Įā”┤µĻć┴ąĄ─Ė³ą┬Ģrķg│¼▀^▓Ņäė╩Įā”┤µĻć┴ąĄ─Č■▒ČĪŻ

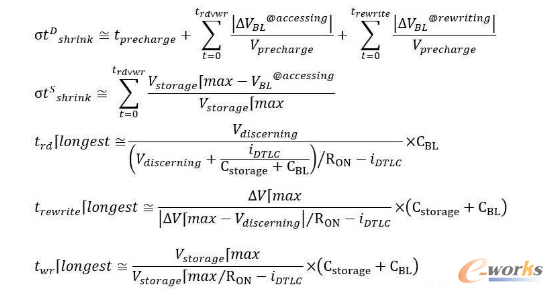

Įøė╔╔Ž╩÷Ą─Ęų╬÷Č°Ą├ų¬ę╗ą®Ģ■ė░ĒæĢrķgĄ─ę“╦žŻ¼ŲõųąŻ¼ą╣┬®ļŖ┴„╩Ūų„ę¬ę“╦žŻ¼▓óŪęš²▒╚ė┌╣żū„£žČ╚ĪŻĻPė┌į┌▓Ņäė╩Įā”┤µĻć┴ąā╚▓┐å╬ę╗å╬į¬Ą─ą╣┬®Ģrķg(tDleakage)ęį╝░į┌å╬Č╦╩Įā”┤µĻć┴ąā╚▓┐å╬ę╗å╬į¬Ą─ą╣┬®Ģrķg(tSleakage)┐╔ė╔ęįŽ┬Ą─öĄīWĘĮ│╠╩ĮüĒ▒Ē▀_Ż¼ŲõųąŻ¼“t_zeroing”┤·▒Ēå╬Č╦╩Įā”┤µå╬į¬į┌├┐┤╬ī”ā”┤µļŖē║ł╠ąąÜw┴ŃĄ─ĢrķgŻ¼ęÓ╝┤åóäėų„äė▒Ż│ų╣”─▄Ą─ĢrķgŻ║

ė╔ė┌├┐«öėąę╗ā”┤µĻć┴ąš²į┌┤µ╚Īų«ĢrŠ═Ģ■ė░Ēæā╚▓┐Ė„ā”┤µå╬į¬Ą─Ė³ą┬ĢrķgŻ¼╦∙ęįŲõėÓā”┤µå╬į¬╩▄ĄĮ▀@ę╗┤µ╚Īū„śIČ°▒╗┐sČ╠┴╦Ė³ą┬ĢrķgŠ═├¹×ķ╩š┐sĢrķgĪŻ▓Ņäė╩Įā”┤µĻć┴ąĄ─╩š┐sĢrķg(σtDshrink)ęį╝░å╬Č╦╩Įā”┤µĻć┴ąĄ─╩š┐sĢrķg(σtSshrink)┐╔ė╔ęįŽ┬Ą─öĄīWĘĮ│╠╩ĮüĒ▒Ē▀_Ż¼ŲõųąŻ¼“t_precharge”┤·▒ĒŅA│õļŖĢrķgŻ¼“t_rdvwr”┤·▒Ēūx╚Ī╗“īæ╚ļĢrķgŻ¼“t_rewrite”┤·▒Ē╗žīæĢrķgŻ║

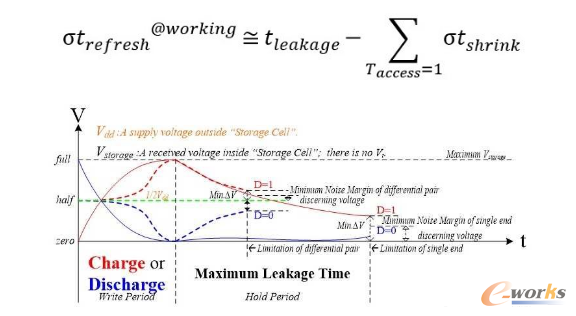

ĻPė┌Ė„ĘNā”┤µĻć┴ąį┌╣żū„ųąĄ─äėæBĖ³ą┬Ģrķg(σt_refresh@working)┐╔ė╔ęįŽ┬Ą─öĄīWĘĮ│╠╩ĮüĒ▒Ē▀_Ż¼▓óŪęäėæBĖ³ą┬Ģrķg▓╗═¼ė┌įOėŗ╔ŽĄ─Ė³ą┬ĢrķgŻ¼ŲõųąŻ¼“T_access”┤·▒Ēł╠ąą┤µ╚Īū„śIĄ─┤╬öĄŻ║

łD4Ż║ā”┤µå╬į¬(▓╗ĦVt)Ą─ā”┤µļŖē║▒╚▌^

łD5Ż║ā”┤µå╬į¬(ĦVt)Ą─ā”┤µļŖē║▒╚▌^

ĮYšō

▓Ņäė╩Įā”┤µĻć┴ąĄ─┤µ╚ĪļŖ┬Ę║▄╚▌ęūĮøė╔┴Ģęį×ķų¬Ą─ļŖ┬ĘüĒīŹ¼FŻ¼╚╗Č°Ż¼å╬Č╦╩Įā”┤µĻć┴ąĄ─┤µ╚Ī╠žąįī”ė┌öĄō■Įė╩šŲ„Ą─įOėŗ╩Ūę╗ųž┤¾Ą─┐╝“ׯ¼ė╔┤╦┐╔═Ųų¬1T1C DRAMå╬į¬į┌│÷¼FęįüĒŠ═╩Ū╩╣ė├▓ŅäėĘ┼┤¾Ų„üĒūx╚ĪöĄō■ĪŻ▒Š╬─ī”ė┌DRAM┤µ╚Ī╝╝ągĄ─Ė─ūāČ°ą╬│╔┴╦▀@ĘNå╬Č╦╩Įā”┤µĻć┴ąŻ¼─╦╩Ū╗∙ė┌ė╔╚²ļŖŠ¦¾wĮY║Ž┴Ēę╗ļŖūĶŲ„╦∙ĮM│╔Ą─SRAMå╬į¬ĪŻ║åčįų«Ż¼ņoæB£p┴┐╝╝ąg│╔Ż¼äėæB┤µ╚Ī╠žąį═¼ĪŻį┌ś╦£╩Ą─CMOSųŲ│╠╝╝ągŽ┬Ż¼«öSRAMå╬į¬Ą─ļŖŠ¦¾wöĄ┴┐£p╔┘ų┴╚²ŅwĄ─Ģr║“Š═╔┘┴╦ą®įŁėąĄ─╠žąįŻ¼ė╚Ųõ╩Ū┤µ╚Ī╠žąįĄ─▐ō«ÉŻ¼▓óŪęŅÉ╦Ųė┌DRAMå╬į¬ĪŻ

║╦ą─ĻPūóŻ║═ž▓ĮERPŽĄĮyŲĮ┼_╩ŪĖ▓╔w┴╦▒ŖČÓĄ─śIäšŅIė“ĪóąąśIæ¬ė├Ż¼╠N║Ł┴╦žSĖ╗Ą─ERP╣▄└Ē╦╝ŽļŻ¼╝»│╔┴╦ERP▄ø╝■śIäš╣▄└Ē└Ē─ŅŻ¼╣”─▄╔µ╝░╣®æ¬µ£Īó│╔▒ŠĪóųŲįņĪóCRMĪóHRĄ╚▒ŖČÓśIäšŅIė“Ą─╣▄└ĒŻ¼╚½├µ║Ł╔w┴╦Ų¾śIĻPūóERP╣▄└ĒŽĄĮyĄ─║╦ą─ŅIė“Ż¼╩Ū▒ŖČÓųąąĪŲ¾śIą┼Žó╗»Į©įO╩ū▀xĄ─ERP╣▄└Ē▄ø╝■ą┼┘ćŲĘ┼ŲĪŻ

▐D▌dšłūó├„│÷╠ÄŻ║═ž▓ĮERP┘YėŹŠWhttp://www.guhuozai8.cn/

▒Š╬─ś╦Ņ}Ż║DRAM║╦ą─įOėŗĄ─ą┬┼f┤µ╚Ī╝╝ąg▓Ņ«É

▒Š╬─ŠWųĘŻ║http://www.guhuozai8.cn/html/consultation/10839321470.html